CMOS Logic Gate - GeeksforGeeks

Jun 6, 2024 · AOI (and-or-invert) and OAI (or-and-invert) gates are two basic configurations that can be realized using CMOS logic. The CMOS realization of these two types of gates is shown …

CMOS Logic Gates Explained - ALL ABOUT ELECTRONICS

Apr 14, 2023 · In this article, CMOS Logic is explained, and how to design different logic gates using CMOS Logic is explained in detail.

Basic CMOS Logic Gates - Technical Articles - EE Power

Oct 27, 2021 · Logic gates that are the basic building block of digital systems are created by combining a number of n- and p-channel transistors. The most fundamental connections are …

CMOS Gate Circuitry | Logic Gates | Electronics Textbook

A CMOS gate also draws much less current from a driving gate output than a TTL gate because MOSFETs are voltage-controlled, not current-controlled, devices. This means that one gate …

AND and OR gate using CMOS Technology - VLSIFacts

Mar 4, 2023 · In this article, we will discuss how to implement 2 input AND and OR gate using CMOS technology. Generally in our academic curriculum, students are taught AND and OR …

CMOS Logic Gate in Digital Electronics - Online Tutorials Library

Here, we have combined multiple CMOS inverters together to build a CMOS OR gate. In the circuit diagram, the CMOS OR gate consists of a PMOS transistor and an NMOS transistor, …

Example: Another CMOS Logic Gate Synthesis Now let’s design a gate that realizes this Boolean algebraic expression: And thus: Y = AB + C′ Therefore, the inputs to this logic gate should be …

CMOS gate circuitry - Electronics teacher

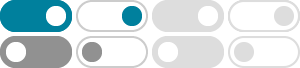

B-series CMOS gates have "buffered" outputs to increase voltage gain from input to output, resulting in faster output response to input signal changes. This helps overcome the inherent …

CMOS OR Gate: Working Principle & Important Applications

May 19, 2023 · When it comes to digital logic circuits, CMOS (Complementary Metal-Oxide-Semiconductor) technology has revolutionized how we design and build gates like the CMOS …

The four terminals of a fet (gate, source, drain and bulk) connect to conducting surfaces that generate a complicated set of electric fields in the channel region which depend on the relative …